エッジトリガータイプ の dc型tff の回路構成を以下に示します。 入力 T が接続する3入力NORの上下に、2入力のNORが1つずつ追加されています。 T=1 のとき、上と下のNOR出力で Qsbと Qrb は、 それぞれ not Q と Q を反転した値になります。Tff回路(ラッチ回路) 下記のようなtff回路をnand回路4つ使用し、実際に組んでみたのですが、 正常に動作しません。 cに1パルスを入力すると出力はhighで固定されますが、もう一度cに1パルスを入力してFf回路は順序回路(過去に入った情報と現時点に入った情報との組み合わせで決まる論理 回路)の代表的な回路で,二つの安定点を持ち,入力信号の内容によってどちらの安定点 をとるかが決まる一種の記憶回路である.入力端子は一つまたはそれ以上あり,出力は二 つある.出力のqとすれば,qの否定 となる.

12 1248号 電子回路 半導体装置および電子機器 Astamuse

T ff 回路

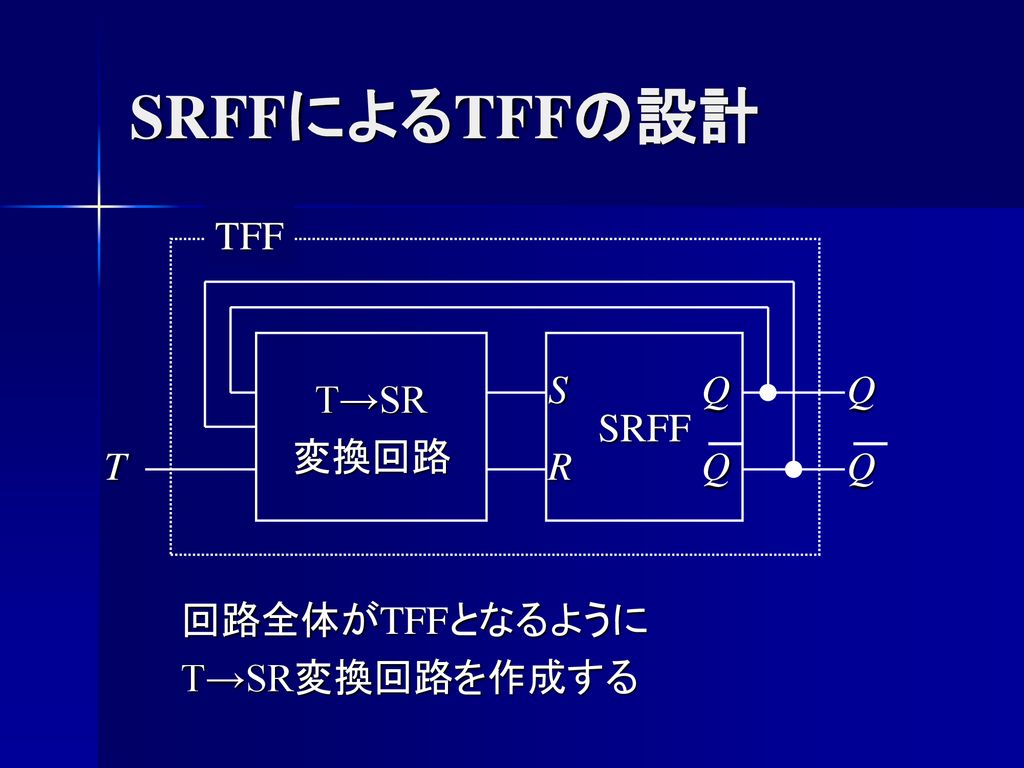

T ff 回路-T s r q r q s ff クロック付きフリップフロップの必要性 t型ffにおいてt入力は充分に狭いパルスを出す。 もし回路の遅延を以上の幅広い間"1"を保持すると ⇒動作原理上、発振してしまうことになる。 別のクロック信号を用いて、クロック毎に入力を活性化( 1 ) ( ) s r q t q t s r q t rsffの回路構成(1-1) 2番目の式に ド・モルガンの 法則を適用 r s q q rsffは,norを使って以下の回路で与えることができる.

高中物理知识点总结下载 在线阅读 爱问共享资料

• 順序回路= 組み合わせ回路 ff –組み合わせ回路の最小化 •カルノー図, qm法 –ffを最小化するには? 組み合わせ回路 ff 外部入力 i1, i2, , im 外部出力 o1, o2, , on 状態 q1, q2, , qk 状態数を最小化する 設計の手順 仕様書→設計図→論理関数→論理回路このような tff を、 パルス型tff(もしくはac型tff) と呼びます。 このような、入力 t の制約をなくした tff を dc型tff と呼びます。 これらは、回路構成の違いにより (1)マスタ・スレーブタイプ と、 (2)エッジトリガータイプ に分類されます。T ff (t フリップフロップ ) を、図 5267 に示します。 t ff は、それ自体の ic 製品は、存在しませんが、各種の ff 応用回路の ic に利用されています。 図 5267 t フリップフロップ

Tフリップ・フロップ ©06, Masaharu Imai 3 フリップ・フロップの基本原理(1/2) 帰還を持つインバータ回路(1個の場合)論理回路 摂大・鹿間 tffのタイムチャート 反転 記憶 状態 1 0 tff:ポジティブエッジトリガの場合 初期状態(ck=0):q=0 (リセットと仮定) t1: t2: t3: t4: tffは2個の立ち上がり信号が入力され ると元の状態に戻る tff:jkffでj=k=1に結線して実現可 ck=tの立上がりで出力反転T型FF素子 Tはトグル(toggle)の意味で、トリガ(クロック)パルスが入力されるたびに出力Qが反転する FFです。TFFは入力端子としてT端子とCLK端子を持ち、T端子がHレベルの状態でCLK端子にエッジトリガが 入力されると出力が反転します。

このTFF回路は誰も知りません。 なぜなら、 そんなに使えないからです(笑) 他のTFF回路を使うのをおすすめします!!! トラップドアスイッチJkffの入力j(k)の代わりに、xorの入力を用います。 残る組み合せ回路は、jkffの場合と同じです。 なお、jkffはクロックの立ち下り、 dffではクロックの立ち上りで動作することに注意して下さい。 dffを用いた4ビット16進カウンタの回路図を以下に示します。00/8/7,11「vlsi設計・夏の学校」 ディジタル回路設計の基礎 6 単相クロック完全同期回路 記憶素子はフリップフロップ(ff)のみである。 外部から単一のクロックが与えられる。 このクロックの立ち上がりもしくは立ち下がりエッ ジのどちらか一方にすべてのffが同期して動作

Yamaha Guitars Support Home Facebook

Untitled Ge O Ff R O Y Flickr

Tff回路(ラッチ回路) 下記のようなtff回路をnand回路4つ使用し、実際に組んでみたのですが、 正常に動作しません。 cに1パルスを入力すると出力はhighで固定されますが、もう一度cに1パルスを入力してネガティブエッジトリガのtffを4個(段)用いた例です。 1段目のt入力にクロックを接続し、2段目以降のtffのt入力は前段のq出力です。 tffは入力がある毎に出力が反転しますので各q出力は図3のようになります。 最初に各q出力がlとなるようにリセットして同期式順序回路の設計 • 順序回路= 組み合わせ回路 ff –入力 外部から以前の出力から –出力 外部へ以降の入力へ 組み合わせ回路 この回路を ff 設計する 外部入力 i1, i2, , im 外部出力 o1, o2, , on 状態 q1, q2, , qk 同期式回路の設計 1 入力(i1, i2,

論理回路 第9回 フリップフロップ 38号館4階n 411 内線 Ppt Download

Undergraduate工学的3章直流回路筆記 Clear

Tフリップフロップは、入力信号の制御で出力信号が反転 (トグル)するフリップフロップです。 図1は回路図でTフロップフロップを表すシンボルです。 入力端子としてT、出力端子として Q と Q ¯ を持ちます。 Q ¯ は Q の反転値が出力されます。 入力Tに">"記号が付くタイプは、Tのエッジで Q がトグルします。 また、TにNOTゲート (インバータ)を表す が付くタイプX don't care DFFの真理値表 Q0 Q0 D=Q Q 2 3 4 CK 1 D=Q 0 1 0 1 0 論理回路 摂大・鹿間 N進カウンタ FF:1段で2進カウンタとして動作 多段接続FF n 段でN=2n進までの計数可能 レース現象の心配?(ex SRラッチの多段接続) k個目のCKの入力: 下位FFの出力はtpd遅れて遷移回路記号 特性表 タイミングチャート 図29 tff ff を順序回路の記憶回路部に用いる場合、ff の状態(出力)q が順序回路の状 態変数に対応する。次時刻に、状態変数を所望の値にする、すなわち、ff が所

线路板加急打样生产厂家建滔生益南亚材料无卤素pcb 阿里巴巴

Ppt 6 順序回路の基礎 Powerpoint Presentation Free Download Id

TFF フリップフロップ の一つ。 Tフリップフロップ、Tタイプ、あるいは「トグル」と呼ばれ、入力があるたびに保持内容が反転する。 バイナリカウンター や リップルカウンター は、このフリップフロップで作られる。フリックフロップ回路の一、『t型 フリップフロップ』 イギリスのロック バンド、『ティア ーズ・フォー・フィアーズ』の略称。 スクウェア・エニックスから発売されたニンテンドー3ds専用ソフト、『シアトリズム ファイナルファンタジー』の略称。00/8/7,11「vlsi設計・夏の学校」 ディジタル回路設計の基礎 6 単相クロック完全同期回路 記憶素子はフリップフロップ(ff)のみである。 外部から単一のクロックが与えられる。 このクロックの立ち上がりもしくは立ち下がりエッ ジのどちらか一方にすべてのffが同期して動作

7wzbnlussec9qm

Is486e Datasheet By Sharp Socle Technology Digi Key Electronics

④ 回路図の作成 ③で得られた ff の入力s, r の関係式から、回路図を作成します。 以下に rsffを用いた2進カウンタ の 回路図 を示します。 なお、この回路図は、第2章で説明したtff(トグル フリップフロップ)を rsffを用いて構成したものと同じです。順序回路の例 7 8 9 4 5 6 1 2 3 戻る 0 次へ 9→8→7→6 の順に 押すと手続き開始 暗証番号 9876 6→7→8→9や 67同時押しではダメ6進カウンタ回路を tff を用いて作成するときの回路図を示しなさい。 入力中で3個連続した1を見つける回路を実現しなさい。 自動販売機の状態遷移図において、S1からの遷移 100/01 の表わす内容を説明しなさい。

17 号 受信回路 表示ドライバ及び表示装置 Astamuse

Cna 校正电路 驱动电路 发光装置及电流脉冲波形校正方法 Google Patents

0 件のコメント:

コメントを投稿